Intel: Pii jäämässä historiaan 7 nm:n tekniikan myötä

Intel on esitellyt San Franciscossa ISSCC 2015 -konferenssissa uusia tutkimustuloksiaan sekä visioitaan tulevaisuuden tuotantotekniikoista.

Intel pääsi kunnolla vauhtiin 14 nanometrin piirien tuotannossa vasta tänä vuonna, vaikka ensimmäisiä piirejä esiteltiinkin paperilla jo viime vuoden puolella. Viivästyneen julkaisun taustalla oli käytännössä se, että uusi tuotantotekniikka osoittautui odotettua monimutkaisemmaksi ja eteen tulleiden ongelmien ratkominen otti aikansa.

ISSCC-esittelyiden perusteella Intel on kuitenkin luottavainen, että vastaavankaltaisilta viivästyksiltä voidaan välttyä tulevaisuudessa kun transistoreita aletaan valmistaa 10 nanometrin tekniikalla. Nykyisen käsityksen mukaan Intel olisi valmis siirtymään 10 nanometrin tekniikkaan vuoteen 2017 mennessä.

Transistoreiden kutistuminen ei pysähdy 10 nanometriin, mutta piin aikakausi saattaa olla katkolla. Intelin näkemyksen mukaan 7 nanometrin tekniikkaan siirtyminen vaatii myös siirtymistä uusiin puolijohdemateriaaleihin, joiden varauksensiirtokyky on parempi kuin piillä.

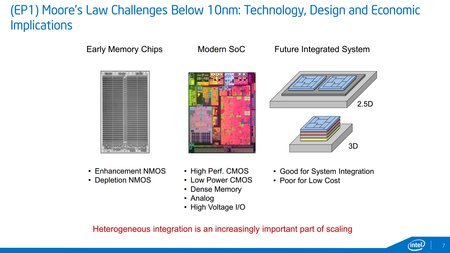

Uusien materiaalien lisäksi Intel tutkii parhaillaan myös 2,5D- ja 3D-paketointimenetelmiä, joissa piirejä voitaisiin asetella samalle alustalle rinnakkain tai päällekäin. Päällekäin pinottavien piirien avulla säästettäisiin erityisesti mobiililaitteissa elintärkeää pinta-alaa, kun eri piirejä ei tarvitsisi levittää eri puolille laitetta.

Intel ei tässä vaiheessa esitellyt suunnitelmiaan seitsemää nanometria pidemmälle, mutta puolijohteiden valmistukseen käytettävien laitteiden kehittäjät joutuvat tietysti ajattelemaan jo tässä vaiheessa pari askelta pidemmälle. Esimerkiksi Applied Materialsin mukaan tulevaisuudessa kolmiulotteiset FinFET-transistorit voidaan korvata pienemmissä viivanleveyksissä uusilla GAA- eli Gate All Around -tyyppisillä transistoreilla.

TÄMÄN UUTISEN KOMMENTOINTI ON PÄÄTTYNYT